7.4 Voltage-Divider Biasing

1. Tujuan [kembali]

a.) Memahami prinsip kerja voltage-divider biasing dan keuntungan dari teknik ini dalam rangkaian transistor.

b.) Mampu merancang dan menganalisis rangkaian voltage-divider biasing yang baik dan efisien.

c.) Memahami persamaan-persamaan yang terdapat dalam voltage-divider biasing

2. Alat dan Bahan [kembali]

a.) Resistor

Resistor adalah komponen elektronika yang berfungsi untuk menghambat atau membatasi aliran listrik yang mengalir dalam suatu rangkaian elektronika.

Berikut adalah simbol resistor dalam bentuk gambar yang sering digunakan dalam suatu desain rangkaian elektronika,

Berikut merupakan nilai resistor berdasarkan kode warna,

Ground adalah titik yang dianggap sebagai titik kembalinya arus listrik arus searah atau titik kembalinya sinyal bolak balik atau titik patokan (referensi) dari berbagai titik tegangan dan sinyal listrik di dalam rangkaian elektronika.

JFET N Channel memiliki lapisan tipis semikonduktor tipe P yang dibentuk di atas substrat tipe N. Lapisan tipis tersebut sering disebut sebagai terminal Gate.

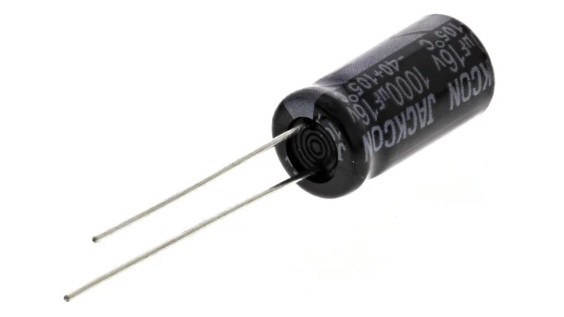

Kapasitor adalah alat yang digunakan untuk menyimpan energi dan arus listrik pada jangka waktu tertentu.

3. Dasar Teori [kembali]

Susunan bias voltage-divider yang diterapkan pada penguat transistor BJT juga diterapkan pada penguat FET seperti yang ditunjukkan oleh Gambar 7.17. Konstruksi dasarnya sama persis, tetapi analisis dc masing-masing sangat berbeda. IG = 0 A untuk penguat FET, tetapi magnitudo IB untuk penguat BJT common-emitter dapat mempengaruhi level dc arus dan tegangan pada kedua sirkuit masukan dan keluaran.

Jaringan rangkaian pada gambar 7.17 digambar ulang seperti yang ditunjukkan pada Gambar 7.18 untuk analisis dc. semua kapasitor telah diganti dengan sirkuit terbuka seperti pada Gambar 7.18b. Sumber VDD dibagi menjadi dua sumber setara karena IG = 0 A, Maka hukum arus Kirchhoff IR1 = IR2. Dan rangkaian seri setara dapat digunakan untuk menemukan nilai VG, Tegangan VG sama dengan tegangan yang melintasi R2 dapat dicari dengan persamaan :

Menerapkan hukum tegangan Kirchhoff searah jarum jam pada loop yang ditunjukkan pada Gambar 7.18 menghasilkan:

Dengan mensubstitusikan ID = 0 mA ke dalam persamaan 3 maka didapatkan nilai VGS :

Hasilnya menentukan bahwa setiap kali kita memplot Persamaan 3 , jika ID = 0 mA, nilai V GS untuk plot akan menjadi VG volt. Seperti gambar berikut :

Untuk titik lainnya, setiap titik pada sumbu vertikal VGS = 0 V. Nilai ID :

Dua titik yang didefinisikan di atas memungkinkan pembuatan garis lurus untuk mewakili Persamaan 3. Karena potongan pada sumbu vertikal ditentukan oleh ID = VG/RS dan VG diperbaiki oleh jaringan masuk, Nilai R S yang meningkat akan mengurangi tingkat potongan ID sebagaimana terlihat pada Gambar 7.19.

Setelai nilai IDQ dan VGSQ ditentukan maka,

4. Percobaan [kembali]

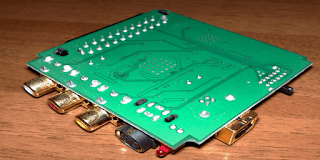

Sumber tegangan AC dengan amplitudo 5 dan frekuensi 1kHz dihubungkan sebagai vi ke kapasitor C1 dan diberi sumber tegangan VDD sebesar 16 V. Diukur tegangan untuk mencari VG dengan menghubungkan voltmeter dari gate terhadap ground didapat 1.67 V. Diukur resistor pada RS didapat 4.42 V. Lalu diukur tegangan VGS dengan mengubungkan voltmeter dari gate dan source didapat -2.75 V lalu diukur arus pada kaki drain didapat 3.66 mA. Lalu dipasang osiloskop pada bagian input dan output untuk mendapatkan gelombang.

Sumber tegangan AC dengan amplitudo 5 dan frekuensi 1kHz dihubungkan sebagai vi ke kapasitor C1 dan diberi sumber tegangan VDD sebesar 16 V. Diukur tegangan untuk mencari VDS dengan menghubungkan voltmeter dari drain terhadap source didapat 6.34 V. Diukur resistor pada RS didapat 4.4 V. Lalu diukur tegangan VGS dengan mengubungkan voltmeter dari gate dan source didapat -2.45 V lalu diukur arus pada kaki drain didapat 3.44 mA.Diukur tegangan VDG dengan menguhubungkan voltmeter ke kari drain dan gate didapat 10.8 V. Lalu dipasang osiloskop pada bagian input dan output untuk mendapatkan gelombang.

5. Video [kembali]

6. Example [kembali]

a.) Tentukanlah nilai dari :

jika ID = IDSS/4 = 8 Ma/4 = 2 mA, maka VGS = VP/2 = -4 V/2 = -2 V. Kurva hasil

yang mewakili Persamaan Shockley muncul pada Gambar 7.22. Persamaan didefinisikan

oleh:

IC = IE = 1,86 mA

Tegangan kolektor – emitter adalah

VCE = VCC – IC(RC + RE) = 30 – 1,86(0,001)9000

= 13,3 V

c.) Tentukan tegangan bias dc Vce dan arus Ic dari konfigurasi voltage-divider pada gambar berikut :

7. Problem [kembali]

1.) Jelaskan prinsip dasar dari voltage divider biasing dan apa keuntungan penggunaan teknik ini pada rangkaian transistor?

Jawaban:

Voltage divider biasing adalah teknik biasing pada transistor yang menggunakan resistor pembagi tegangan (voltage divider) untuk menghasilkan tegangan bias pada basis transistor. Prinsip dasarnya adalah mengalirkan arus tetap melalui resistor pembagi tegangan yang kemudian menghasilkan tegangan DC tetap yang digunakan sebagai bias pada basis transistor. Keuntungan penggunaan teknik ini adalah kemampuannya untuk menghasilkan level bias yang stabil dan dapat diatur secara presisi pada transistor, sehingga dapat meningkatkan akurasi dan performa dari rangkaian transistor.

2.) Bagaimana cara menghitung nilai resistor pada voltage divider biasing?

Untuk menghitung nilai resistor pada voltage divider biasing, dapat menggunakan rumus sebagai berikut:

R1 = (VCC - VBE) * β / IB

R2 = (VCE - VBE) / IB - R1

Dimana:

VCC = tegangan suplai

VBE = tegangan basis-emitter

VCE = tegangan kolektor-emitter

β = hFE, gain dari transistor

IB = arus basis

3.) Jelaskan bagaimana cara menentukan titik kerja (quiescent point) pada rangkaian transistor yang menggunakan voltage divider biasing?

Untuk menentukan titik kerja pada rangkaian transistor yang menggunakan voltage divider biasing, langkah-langkahnya adalah sebagai berikut:

- Hitung nilai resistor R1 dan R2 menggunakan rumus yang sudah dijelaskan pada nomor 2.

- Hitung nilai arus basis (IB) menggunakan rumus IB = IC / β.

- Hitung nilai arus kolektor (IC) menggunakan rumus IC = β * IB.

- Hitung nilai tegangan kolektor (VC) menggunakan rumus VC = VCC - (IC * RC).

- Hitung nilai tegangan basis (VB) menggunakan rumus VB = VBE + (IB * R1).

- Hitung nilai quiescent point (Q) menggunakan rumus Q = (VC, IC, VB).

- Setelah titik kerja ditentukan, maka dapat dilakukan analisis lebih lanjut pada rangkaian transistor.

8. Pilihan Ganda [kembali]

a.) Apa yang dimaksud dengan voltage-divider biasing?

a. Pembagian arus

dalam rangkaian listrik

b. Pembagian

tegangan dalam rangkaian listrik

c. Pengaturan

tegangan input pada transistor

d. Pengaturan arus

output pada transistor

e. Pengaturan

resistansi dalam rangkaian listrik

b.) Pada pembiasan voltage-divider, apa fungsi dari resistor R1 dan R2?

a. Membagi arus

input

b. Membagi

tegangan input

c. Mengatur arus output

d. Mengatur

tegangan output

e. Mencegah arus

mundur dalam rangkaian

c.) Bagaimana cara menghitung tegangan gate-source (VGS) pada pembiasan voltage-divider?

a. Dengan

mengalikan arus basis (IB) dengan resistansi input (Rin)

b. Dengan

mengalikan arus drain (ID) dengan resistansi output (Rout)

c. Dengan

mengalikan tegangan input (VIN) dengan resistansi input (Rin)

d. Dengan

menggunakan aturan pembagi tegangan (voltage-divider rule) pada resistor R1 dan

R2

e. Dengan

menggunakan aturan Kirchhoff pada loop input dan loop output

9. Link Download [kembali]

File HTML [Download]

Rangkaian 7.17 [Download]

Rangkaian 7.18 [Download]

Rangkaian 7.21 [Download]

Video Rangkaian Rangkaian 7.17 [Download]

Video Rangkaian Rangkaian 7.18 [Download]

Video Rangkaian Rangkaian 7.21 [Download]

Data Sheet JFET [Download]

Data Sheet Resistor [Download]

Data Sheet Baterai [Download]

Tidak ada komentar:

Posting Komentar